3.0 零散点

易错点

- 存取时间和存取周期的区别

- Cache 全写法 和 写回法

- 虚拟存储中主存和辅存的数据调动需要操作系统和硬件共同完成

- DRAM密度比SRAM高,集成度也比SRAM高

- 支持 随机存取 的不一定是 随机存取存储器,ROM通常也支持随机存取

- DRAM 刷新占用一个存储周期(一次访存)

- 提高刷新存储器的带宽方式:采用DRAM或SRAM(如果需求空间小);采用多体交叉存储结构;内部总线宽度提升;用双端口存储器将刷新与更新端口分开

- DRAM中存取周期对应于一行,所以计算刷新时间则乘以行数

- Cache 直接映射下,物理地址划分为:主存字块标记+Cache字块标记+块内地址

- 仅 主存字块标记 需要保存在 Chache 中

- LRU 记录使用的位数=\(log_2(n)\) n为相联路数,这样可以区分出唯一的最近使用者

- MAR位数由设计的主存地址空间大小决定,不受主存储器大小影响

- 减少DRAM刷新开销应减少行数

名词概念

- TLB命中、Page命中、Cache命中

- 虚拟地址、实地址、虚页号、叶框号、标记位

3.1 存储器概述

分类

- 按作用或层次分类

- 主存储器:内存

- 辅助存储器:外存

- 高速缓冲存储器:缓存

- 按介质分类

- 磁表面存储器

- 磁心存储器

- 半导体存储器

- 光存储器

- 按存取方式分类

- 随机存储器 RAM

- 只读存储器 ROM

- 串行访问存储器 DAM

- 顺序存取存储器(磁带)

- 直接存取存储器(磁盘)

- 介于顺序和随机之间

- 按信息保存性分类

- 易失性存储器

- 非易失性存储器

性能指标

- 存储容量

- 单位成本

- 存储速度

- 存取时间:启动至完成操作的时间

- 存取周期:两次操作之间需要的最短时间,可能会相比于存取时间再多一个恢复时间

- 主存带宽:传输速率

3.2 存储器的层次化结构

多级存储器

3.3 半导体随机存储器

DRAM和SRAM

- SRAM (Static RAM)

- 六晶体管MOS

- DRAM(Dynamic RAM)

- 电容

- 刷新(2ms丢失)

- 刷新方式

- 集中刷新

- 分散刷新

- 异步刷新

- 对CPU透明

- 刷新方式

- 存储器的读写周期

- RAM读时间(\(t_A\))

- 从给出有效地址到所选内容稳定出现的读时间 \(t_A\) 。期间地址信号和 \(overline{CS}\) 需保持稳定

- 读周期(t_{RC})

- 两次连续读操作的必要间隔时间,大于读时间

- RAM读时间(\(t_A\))

- RAM 的写周期

ROM

- 特性

- 通常结构简单,存储密度通常比可读可写存储器高

- 支持随机存写

- 分类

- MROM(Mask ROM)

- PROM(Programmable ROM)

- EPROM(Erasable Programmable ROM)

- Flash Memory

- SSD(Solid State Drives)

主存的组成

- 编址方式

- 按字

- 按字节(通常方式)

- 容量

- 地址线数量 \(N_{AD}\) 与数据线数量 \(N_D\) 共同决定芯片容量:2^{N_{AD}}*N_D

- 引脚

- 数据线

- 地址线

- 片选 CS

- 或 行选通+列选通 (在地址复用的情况下)

- 写使能 $latex topline{WE}

- 读使能 RD

3.4 主存储器与 CPU 的连接

连接方式

- 数据总线

- 位数与频率正比于数据传输率

- 地址总线

- 决定最大寻址空间

- 控制总线

- 读/写

主存容量扩展

- 位扩展法

- 同一个地址,但代表不同位,使位变多

- 字扩展法

- 由片选信号区分各地址范围,不同地址对应不同存储器的字,使字变多

- 字位同时扩展法

存储芯片的地址分配和片选

- CPU 访问

- 首先选择芯片,即片选

- 然后选择相应的存储单元,即字选

- 线选法

- 优点

- 不需要译码器

- 缺点

- 地址不连续

- 优点

- 译码片选法

存储器与CPU的连接

- 合理选择存储芯片

- 地址线的连接

- 数据线的连接

- 读写命令线的连接

- 片选线的连接

3.5 双端口 RAM 和多模块存储器

双端口 RAM

- 有左右两个独立的端口,允许两个独立的控制器同时异步访问存储单元,当两个端口的地址不同时,不会发生冲突

多模块存储器

- 单体多字存储器

- 一次性读出连续的多个字

- 多体并行存储器

- 高位交叉编址

- 仅仅扩展了字,但还是串行存取

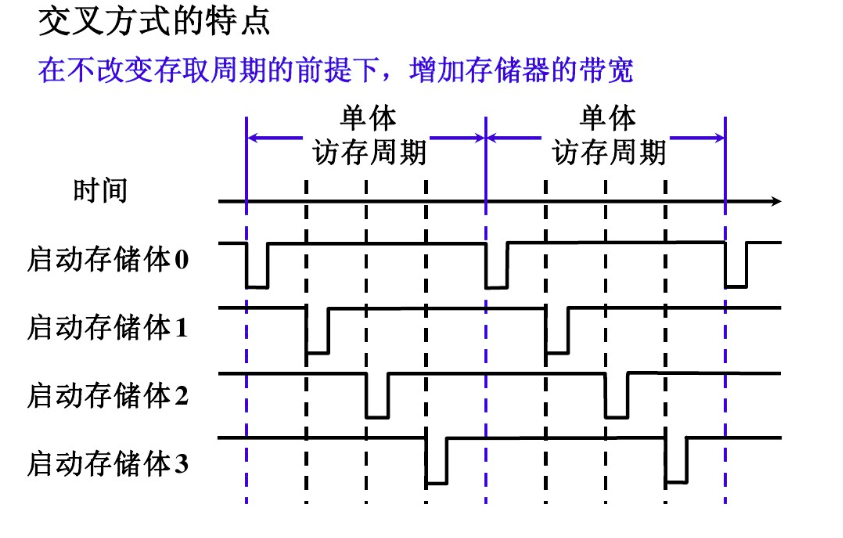

- 低位交叉编址

- 流水线存取,提高读取效率

- 批量读取耗时 \(T+(n-1)t\),其中 T 为存取周期,t 为总线传输周期

- 高位交叉编址

3.6 高速缓冲存储器

程序访问的局部性原理

Cache 基本工作原理

- 块:若干字节组层

- 命中率

Cache 和主存的映射方式

- 直接映射

- 主存中的每一块只能装入 Cache 中的唯一位置

- 可以直接取余

- 全相联映射

- 通常需要按内容寻址

- 组间相联映射

- 组间采取直接映射,组内采取全相联映射

Cache 中主存块的替换算法

- 针对于全相联映射和组相联映射

- 常用算法

- RAND 随机算法

- FIFO 先进先出算法

- LRU 最近最少使用算法

Cache 写策略

- 命中

- 全写法

- 可配合写缓冲

- 写回法

- 每个 Cahce 块需要设置一个脏位标志

- 全写法

- 失效

- 写分配法

- 非写分配法

3.7 虚拟存储器

基本概念

- 将主存与辅存统一编址

- 编程允许涉及的地址为虚地址或逻辑地址

页(Page)式虚拟存储器

- 以页为基本单位

- 名词

- 实页:主存中的页

- 虚页:不在主存中的页

- 页表:实页号和虚页号的对照关系

- 带有效位、脏位、引用位、物理或磁盘地址

快表(TLB:Translation lookaside buffer)

- 将主存中的部分页表存于Cache中

段式存储器

- 根据程序实际需要长度进行记录

段页式虚拟存储器

- 用以页为最小单位的段

- 优点

- 便于管理,不易浪费

- 缺点

- 需要两次查表